# FAST SIMULATION OF COMPUTER ARCHITECTURES

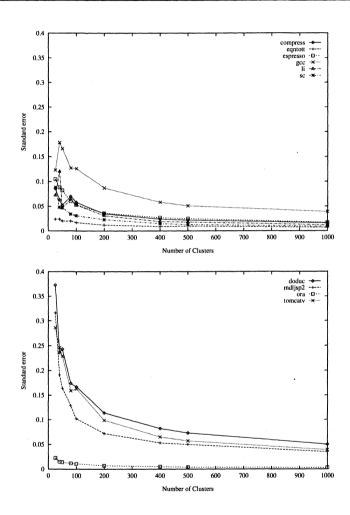

edited by THOMAS M. CONTE CHARLES E. GIMARC

SPRINGER SCIENCE+BUSINESS MEDIA, LLC

# FAST SIMULATION OF COMPUTER ARCHITECTURES

# FAST SIMULATION OF COMPUTER ARCHITECTURES

#### EDITED BY

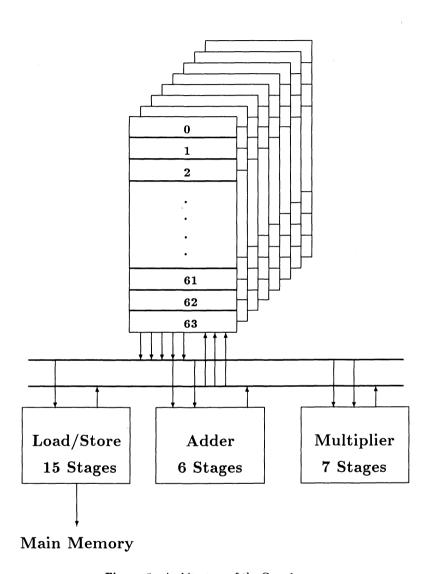

Thomas M. Conte University of South Carolina Columbia, South Carolina

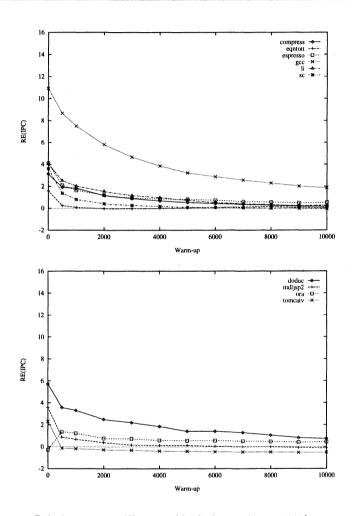

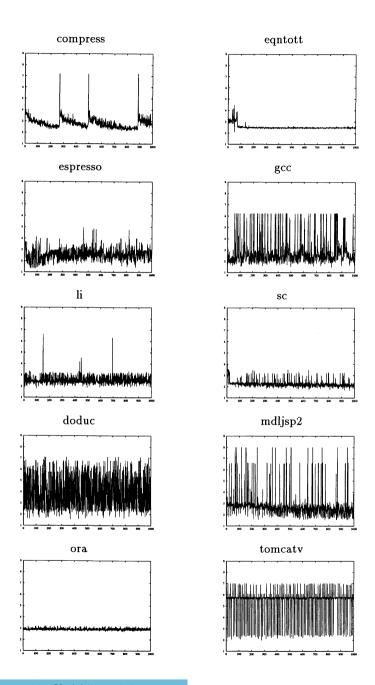

Charles E. Gimarc

AT&T Global Information Solutions

West Columbia, South Carolina

SPRINGER SCIENCE+BUSINESS MEDIA, LLC

#### Library of Congress Cataloging-in-Publication Data

Fast simulation of computer architectures / edited by Thomas M. Conte, Charles E. Gimarc.

p. cm.

Includes bibliographical references and index.

ISBN 978-1-4613-6002-5 ISBN 978-1-4615-2361-1 (eBook)

DOI 10.1007/978-1-4615-2361-1

Computer architecture--Evaluation.

Digital computer simulation.

Conte, Thomas M., 1964 II. Gimarc, Charles E., 1953-

QA76.9.A73F28 1995 004.2'4'011--dc20

95-19087

CIP

Copyright © 1995 by Springer Science+Business Media New York Originally published by Kluwer Academic Publishers in 1995 Softcover reprint of the hardcover 1st edition 1995

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher, Springer Science+Business Media, LLC.

Printed on acid-free paper.

# CONTENTS

| 1      | INTRODUCTION                                 |    |

|--------|----------------------------------------------|----|

|        | Thomas M. Conte and Charles E. Gimarc        | 1  |

| 2      | SHADE: A FAST INSTRUCTION-SET                |    |

|        | SIMULATOR FOR EXECUTION PROFILING            |    |

|        | Bob Cmelik, David Keppel                     | 5  |

|        | 1 Introduction                               | 5  |

|        | 2 Related Work                               | 7  |

|        | 3 Analyzer Interface                         | 16 |

|        | 4 Implementation                             | 17 |

|        | 5 Cross Shades                               | 28 |

|        | 6 Performance                                | 30 |

|        | 7 Conclusions                                | 35 |

|        | 8 Acknowledgements                           | 35 |

| 3      | INSTRUMENTATION TOOLS                        |    |

|        | Jim Pierce, Michael D. Smith, Trevor Mudge   | 47 |

|        | 1 Introduction                               | 47 |

|        | When To Instrument Code                      | 51 |

|        | 3 How Late Code Modification Tools are Built | 56 |

|        | 4 Current Instrumentation Tools              | 68 |

| 4      | STACK-BASED SINGLE-PASS CACHE                |    |

|        | SIMULATION                                   |    |

|        | Thomas M. Conte                              | 87 |

|        | 1 Introduction                               | 87 |

|        | 2 Single-Pass Cache Simulation               | 88 |

| يشارات | الم للاس                                     |    |

|        |                                              |    |

|        | <ul> <li>3 Extensions to Single-Pass Techniques</li> <li>4 Concluding remarks</li> </ul> | 96<br>103 |

|--------|------------------------------------------------------------------------------------------|-----------|

| 5      | NON-STACK SINGLE-PASS SIMULATION                                                         |           |

|        | Rabin A. Sugumar, Santosh G. Abraham                                                     | 109       |

|        | 1 Introduction                                                                           | 109       |

|        | 2 Fully-associative Cache Simulation                                                     | 111       |

|        | 3 Binomial Forest Simulation                                                             | 117       |

|        | 4 Write-buffer Simulation                                                                | 128       |

|        | 5 Directions for future work                                                             | 139       |

| 6      | EXECUTION DRIVEN SIMULATION OF                                                           |           |

|        | SHARED MEMORY MULTIPROCESSORS                                                            |           |

|        | Bob Boothe                                                                               | 145       |

|        | 1 Introduction                                                                           | 145       |

|        | 2 Implementation Decisions                                                               | 147       |

|        | 3 Example Simulators                                                                     | 152       |

|        | 4 Code Augmentations                                                                     | 154       |

|        | 5 The Simulator Half                                                                     | 160       |

|        | 6 Performance Characteristics                                                            | 162       |

|        | 7 Summary                                                                                | 166       |

| 7      | SAMPLING FOR CACHE AND PROCESSOR SIMULATION                                              |           |

|        | Kishore N. Menezes                                                                       | 171       |

|        | 1 Introduction                                                                           | 171       |

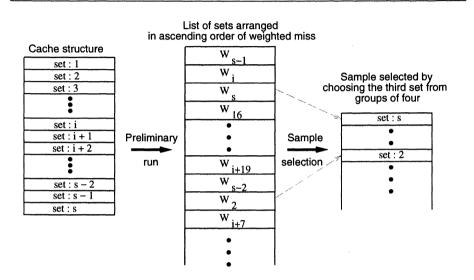

|        | 2 Statistical Sampling                                                                   | 172       |

|        | 3 An Example                                                                             | 184       |

|        | 4 Concluding Remarks                                                                     | 199       |

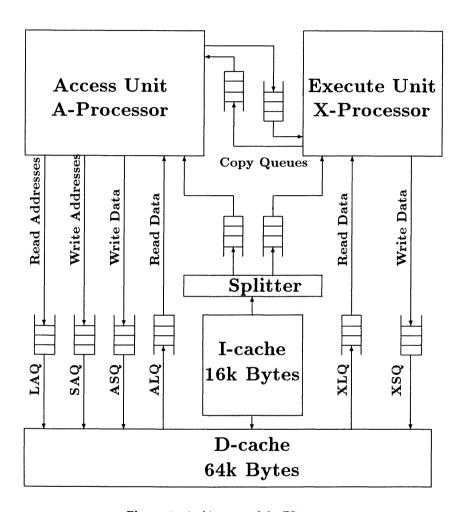

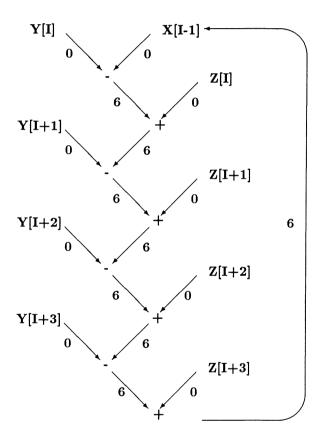

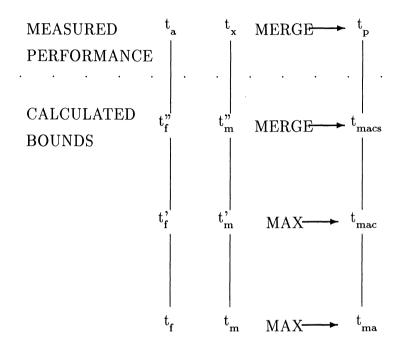

| 8      | PERFORMANCE BOUNDS FOR RAPID COMPUTER SYSTEM EVALUATION                                  |           |

|        | Bill Mangione-Smith                                                                      | 205       |

|        | 1 Introduction                                                                           | 205       |

|        | 2 Outline of Approach                                                                    | 207       |

| تشارات | 3 Simple Bounds Model                                                                    | 211       |

| 4    | Data Dependence And Scalar CPUs        | 217 |

|------|----------------------------------------|-----|

| 5    | MACS: A Hierarchical Performance Model | 226 |

| 6    | Conclusion                             | 234 |

| INDE | x                                      | 239 |

vii

Contents

# **CONTRIBUTORS**

Santosh G. Abraham Hewlett-Packard Laboratories Palo Alto, California

**Bob Boothe**University of Southern Maine

Portland, Maine

Bob Cmelik Sun Microsystems, Incorporated Mountain View, California

David Keppel University of Washington Seattle, Washington

Bill Mangione-Smith University of California at Los Angeles Los Angeles, California

Kishore N. Menezes University of South Carolina Columbia, South Carolina

Trevor N. Mudge University of Michigan Ann Arbor, Michigan

Jim Pierce University of Michigan Ann Arbor, Michigan

Michael Smith Harvard University Cambridge, Massachusetts Rabin A. Sugumar Cray Research Inc. Chippewa Falls, Wisconsin

#### INTRODUCTION

This is a book about sophisticated techniques for simulating computer architectures. It is intended for two groups of readers: the practicing computer architect who is looking for good solutions to tough evaluation problems, and the computer architecture student who would like to augment knowledge obtained from more traditional architecture textbooks. It can also be used as a second textbook for first- or second-semester architecture courses. To this end, each chapter includes 10 to 20 exercises useful as class assignments or as study aids.

It has often been said that computer architecture is not a quantitative, systematic design process, rather it is an art form. There is some truth to this observation. Engineering design involves several steps: (1) innovating potential designs, (2) evaluating the performance of the designs, and (3) selecting the best design. The initial innovation (step (1)) involves creativity. The later evaluation and construction steps can largely be expressed as optimization problems, which are often solved systematically (although tremendous creativity is often applied to devising optimization techniques).

Unfortunately, there is no general theory for systematic computer architecture evaluation and selection. This is partly due to the complexity of the problem: successful general-purpose computer systems must have the capacity for a very diverse set of applications. The workloads used in the design process must capture this diversity. (The field of workload characterization addresses this problem.) Once a workload has been determined, one must face another, more pressing problem. The number of potential designs is large. Consider a uniprocessor workstation. The design of the memory system must be determined. So must the capacity of the network, the disk, any interconnecting

channels, and the processor itself. If the processor is also being designed, the number of variables increases dramatically: the processor pipeline, the branch handling scheme, the role of the compiler, etc. The fact that the workload must be large in order to capture diversity further frustrates the evaluation problem. Fast, efficient, and accurate evaluation techniques are essential for systematic, quantitative computer architecture design.

This book presents several powerful techniques to evaluate the performance of common design tradeoffs. We have attempted to collect what are the most-common and useful of these approaches. We have also included two chapters on how to collect the workload trace itself, since this problem is inextricably intertwined with the evaluation problem.

In Chapter 2, Cmelik and Keppel discuss the basic concepts of instruction-level computer system simulation. This introduction includes a summary and comparison of over 45 modern simulators, virtual machines, and tracing tools. Simulators run target system programs on a host machine. The authors note that simulation is useful for analysis, design, and tuning of HW and SW systems, permitting feedback to improve the design before implementation of ideas. Shade is given as an example of tracing and simulation tools. Shade combines tracing, simulation, and analysis capabilities in a single tool, eliminating the need for multiple tools, and providing high performance. Various levels of functionality are implemented in the variety of tools available. Some features such as tracing signals, self-modifying code, dynamic links, system mode, data references, and tracing speculative execution are typical of most tracing environments. Shade provides some of these features along with the capability for cross-compilation, and several tracing and simulation speed enhancements.

The ability to gather run-time information of executing programs is central to the simulation and analysis of computer architectures and the optimization of applications. In Chapter 3, Pierce, Smith and Mudge present a survey of methods for collecting trace and run-time information. These instrumentation tools typically modify the program under study, either at the compiler level or at the object module level. Once the altered program is run, it generates traces or profile statistics, at some cost in program performance. Examples of source-code, link-time, and executable modification are given. Late-code modification techniques are treated in detail, as they are widely used, and typically the most challenging to implement. Eight of these tools are described and compared. Since instrumentation of multitasking applications and operating system kernels have their own set of unique problems, two of these tools are discussed separately. Instrumentation tools are typically tied to a specific

Introduction 3

ISA. This chapter contains examples of tools useful on MIPS, ALPHA, ix86, RS/6000, PA-RISC, 68000, and SPARC architectures.

Cache and memory system analysis can be either analytical or trace driven. The analytical techniques have the advantage of speed - permitting analysis of a large design space. Their disadvantage is relatively poor accuracy. High accuracy is very important in cache performance analysis since the absolute hit rates are typically very close to 100%. Fast simulation techniques are often required.

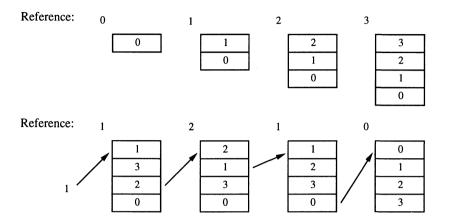

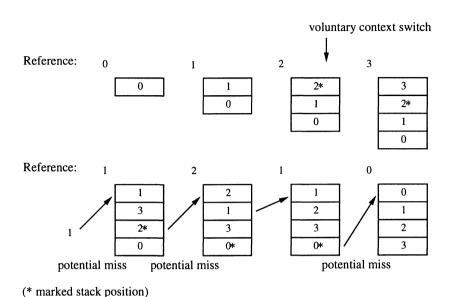

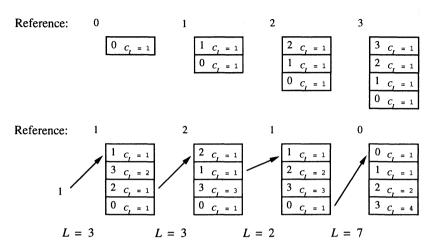

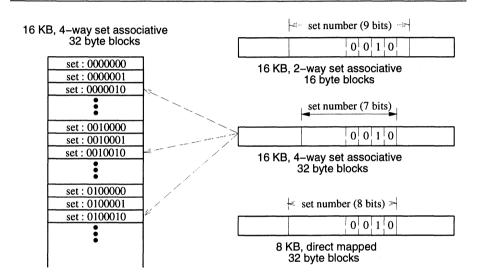

In Chapter 4, one of the editors (Conte) describes the single-pass, stack-based cache simulation technique. Stack-based simulation is desirable for several reasons. First, since it is a single-pass method, its speed permits performance measurement of a large number of cache and memory system designs in one step. Second, since many caches can be evaluated simultaneously, its speed permits use of traces of long-running benchmarks. Chapter 4 explains a specific stack-based approach, the recurrence/conflict method. Many extensions to stack-based techniques have been proposed. The chapter discusses one in detail: an extension to capture the effects of multiprogramming. Algorithm psuedo code and examples are used to present the technique.

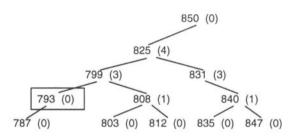

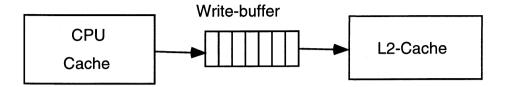

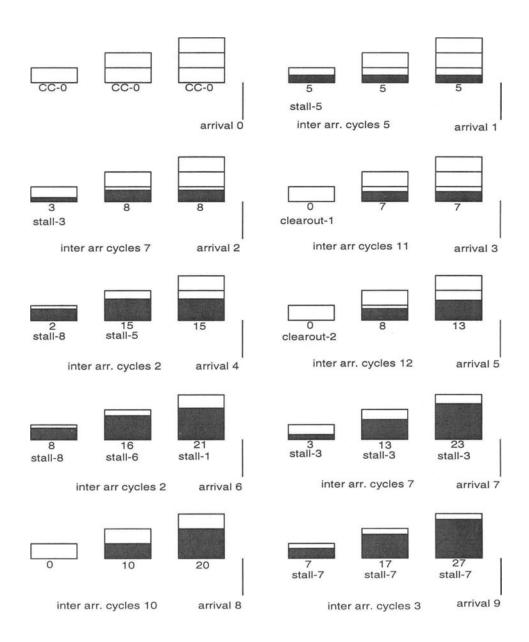

Alternatives to the stack-based simulation algorithms of Chapter 4 are presented in Chapter 5 by Sugumar and Abraham. These non-stack-based single-pass methods rely on *m*-ary trees. The theory of these techniques are used to develop new simulation algorithms for caches and write buffers.

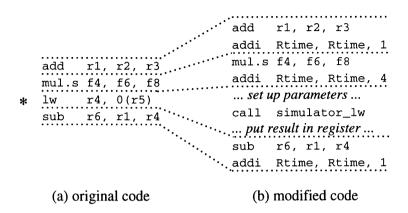

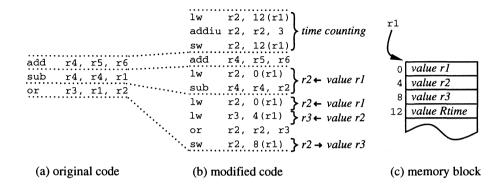

One of the highest performance simulation methodologies is execution-driven simulation. Of these, the highest-performance execution-driven simulators do only the work that is required to obtain the desired results. Additional uninteresting events are not simulated, but are accounted for in other ways. In Chapter 6, Boothe presents three multiprocessor execution-driven simulators and explains their fundamental design choices. Simulation design decisions include techniques for preprocessing (insertion of probe instructions in the application), and execution of select application instructions on a model of the target system while gathering statistics of that execution. Details are given for one simulator in particular, the author's FAST simulator. FAST runs on a uniprocessor host and simulates shared memory multiprocessors.

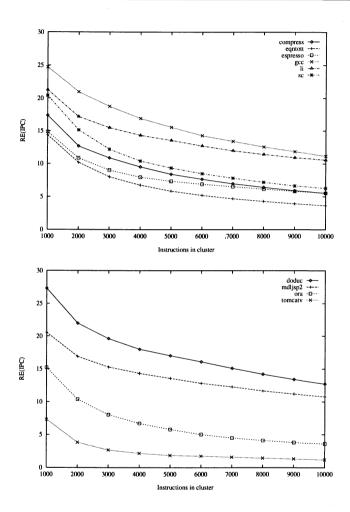

Simulation is often performed to capture a few, key performance metrics. These metrics are summary statistics. In Chapter 7, Menezes explores techniques to speed up simulation by using statistical sampling theory to approximate the summary statistics. The general theory of sampling is presented, followed

المنسلون الاستشارات

by a literature review of cache and processor statistical sampling methods. Menezes then develops a new method for processor sampling and discusses its applications.

In Chapter 8, Mangione-Smith prevents research in establishing performance upper bounds. Bounds are an attractive alternative to simulation for either tuning existing systems or designing new systems. In the context of the research, these bounds are computed for well-behaving scientific kernels. Examples evaluate performance of a subset of the Livermore Fortran Kernels executing on a wide range of computers (Cray-1, Cray X-MP, Cray-2, Convex C-240, Astronautics ZS-1, RS/6000 and MIPS R2000). A hierarchical methodology of computing these bounds is presented. Each level provides a more detailed analysis, yielding tighter, more accurate bounds. Of course, the tradeoff is in analysis effort versus results accuracy. In its current state, this analysis is useful for comparing expected performance with achievable performance with measured performance of applications on specific system implementations. Such comparison could point to optimization opportunities.

Instructors using this book for can teach largely in the order of occurance of the chapters in the text. However, for specific focus on tracing, Chapters 2 and 3 are recommended, with partial coverage of Chapter 6. A treatment of cache and memory hierarchy simulation should include Chapters 4, 5 and 7. A course that focuses on supercomputer architecture should include special attention to Chapters 6 and 8, in addition to the above chapters.

This book has been constructed with close interaction between the authors and editors. We would like to thank the chapter authors for adjusting their texts when we saw conflicts, and working above and beyond the call of duty to help us deliver a coherent, cohesive volume on fast architectural simulation.

This book would not have been possible without the patient and helpful aid of our editor, Alexander Greene. The preliminary work for this book was motivated by a successful session we organized at the *Hawaii International Conference on System Sciences*. The crowd that attended was lively and provided all with a high-quality discussion. In addition to the chapter authors who attended that session, we would also like to thank: Si-En Chang (Chung Yuan University), Gary Lauterbach (Sun Laboratories), Mario Nemirovsky (University of California, Santa Barbara), Jim Smith (University of Wisconsin), Patricia Teller (New Mexico State University), and Larry Wittie (SUNY-Stony Brook).

-TMC and CEG

# SHADE: A FAST INSTRUCTION-SET SIMULATOR FOR EXECUTION PROFILING Bob Cmelik\*, David Keppel†

\*Sun Microsystems, Incorporated, Mountain View, California

†University of Washington, Seattle, Washington

#### 1 INTRODUCTION

Simulation and tracing tools help in the analysis, design, and tuning of both hardware and software systems. Simulators can execute code for hardware that does not yet exist, can provide access to internal state that may be invisible on real hardware, can give deterministic execution in the face of races, and can produce "stress test" situations that are hard to produce on the real hardware [4]. Tracing tools can provide detailed information about the behavior of a program; that information is used to drive an analyzer that analyzes or predicts the behavior of a particular system component. That, in turn, provides feedback that is used to improve the design and implementation of everything from architectures to compilers to applications. Analyzers consume many kinds of trace information; for example, address traces are used for studies of memory hierarchies, opcode and operand usage for superscalar and pipelined processor design, instruction counts for optimization studies, operand values for memoizing studies, and branch behavior for branch prediction.

Simulators and tracing tools appear at first to perform very different tasks. Simulators allow a host machine to run programs written for some target machine, while tracing tools collect run-time information about a program's execution. In practice, though, simulators and tracing tools do much the same work: both are concerned with machine-level details of a program's run-time behavior. For example, simulators and tracing tools often both capture the application's program counter. Likewise, simulation and tracing are often implemented using similar techniques. For example, simulators and tracing tools often work by analyzing the original program instructions and cross-compiling them to sequences of instructions that simulate or trace the original code.

For the purposes of this chapter, then, we can consider simulation and tracing as two facilities provided by a single tool. Several features can improve the utility of such a tool. First, the tool should be easy to use and avoid dependencies on particular languages and compilers. Ideally it should also avoid potentially cumbersome preprocessing steps. Second, it should operate on a wide variety of applications including those that use signals, exceptions and dynamically-linked libraries. Third, trace generation should be fast, both so that traces can be recreated on demand, instead of being archived on bulk storage, and so that it is possible to study realistic workloads, since partial workloads may not provide representative information [6, 7]. Fourth, a tracing tool should provide arbitrarily detailed trace information so that it is useful for a wide variety of analyzers; in general, this means that it must be extensible [58, 59] so that it can be programmed to collect specialized information. Finally, it should be possible to run and trace applications for machines that do not yet exist.

These features are often at odds with each other. For example, static cross-compilation can produce fast code, but purely static translators cannot simulate and trace all details of dynamically-linked code. Also, improved tracing flexibility generally means reduced performance. An interpreter that saves address trace information may be reasonably fast, but adding control over whether it saves an address trace will slow the simulation, if at every instruction the simulator must check whether to save trace information. Providing finer control over where to save trace data slows simulation even more; adding the flexibility to save other kinds of trace information slows simulation yet further.

Because of the conflict between generality and performance, most tools provide only a subset of the features listed above. Shade is a simulation and tracing tool that provides the features together in one tool and uses five general techniques to achieve the needed flexibility and performance. First, Shade dynamically cross-compiles executable code for the target machine into executable code that runs directly on the host machine. Second, the host code is cached for reuse so that the cost of cross-compiling can be amortized. Third, simulation and tracing code are integrated so that the host code saves trace information directly as it runs. Fourth, Shade gives the analyzer detailed control over what is traced: the tracing strategy can be varied dynamically by opcode and address range. Shade then saves just the information requested by the analyzer, so clients that need little trace information pay little overhead. Finally, Shade is extensible: it can call special-purpose, analyzer-supplied code to extend Shade's default data-collection capabilities.

Shade uses these techniques together to perform many useful tasks in combination. Shade performs cross-architecture simulation, collects many kinds of trace information, allows fine control over the tracing, is extensible, and simulates and traces the target machine in detail, including tricky things like signals and self-modifying code. Despite its flexibility, Shade has performance competitive with tools that just cross-simulate without tracing, with tools that do only simple tracing, and even with those that omit details to improve simulation and tracing efficiency. Thus, this study of Shade shows how a general-purpose tool can be made efficient enough to effectively replace many other tools. This chapter also presents a framework for describing simulation and tracing tools.

#### 2 RELATED WORK

This section describes related work and summarizes the capabilities and implementation techniques of some other simulators, virtual machines and tracing tools. In most cases we try to evaluate the capabilities of each tool's technology, but as we are evaluating particular tools, we sometimes (necessarily) evaluate limits of a specific implementation.

# 2.1 Capabilities and Implementation

Table 1 summarizes the capabilities and implementations of a number of tools. The columns show various features of each tool and are grouped in three sections. The first group, *Purpose* and *Input Rep.* describe the purpose of the tool and how a user prepares a program in order to use the tool. The second group *Detail*, *MD*, *MP*, *Sig.* and *SMC OK*, shows the level of detail of the simulation and tracing, and thus the kinds of programs that can be processed by the tool. The third group *Technology*, and *Bugs OK* show the implementation technology used and the tool's robustness in the face of application errors.

Purpose describes how the tool is used: for cross-architecture simulation (sim); debugging (db); for address tracing or memory hierarchy analysis (atr); or for other, more detailed kinds of tracing (otr). Tools marked  $tb_C$  are tool-building tools that provide analyzers with access to arbitrary state of the simulated target machine; the subscript C indicates that they usually use C as the extension language [58, 59].

Table 1 Summary of some related systems. (Continued next page)

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                           | Purpose             | Input<br>Rep. | Detail | MD | MP    | Sig. | SMC | Technology | Bugs<br>OK  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------|---------------|--------|----|-------|------|-----|------------|-------------|

| tutr exe us $Y Y = Y Y$ Ib exe u $X Y Y = Y Y Y$ It tr/otr exe u $X Y Y = Y Y Y$ It tr corr exe u $X Y Y = Y Y Y$ It tr corr exe u $X Y Y = Y Y Y$ It tr corr exe u $X Y Y = Y Y Y$ It tr corr exe u $X Y Y = Y Y Y$ It tr corr exe u $X Y Y = Y Y Y$ It tr corr exe u $X Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | sim                       |                     | exe           | sn     | Y  | z     | Y    | S   | scc+ddi    | Y           |

| thr exe us $Y = Y = Y = Y$ Ib exe u N N N N Y  tr/otr exe u N N N S Y  tr/otr exe u N N N S Y  asm u N N N S Y  tr/otr exe u N N N Y  ib atr/otr/tbc exe usd Y  ib exe u N N N Y  ib atr/otr/tbc exe usd Y  ib exe u N N N Y  ib atr/otr/tbc exe u N N N N N N  ib exe u N N N N N N N N N N N N N N N N N N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $^{\mathrm{tp}}$          | 6                   | exe*          | sn     | z  | z     | ≻    | S   | ang        | Z           |

| otr bill u N Y N Y  otr bill u N N N N Y  otr exe u N N N S Y  exe u N N N Y  exe u N N N Y  otr exe u N N N Y  atr  otr exe u N N N Y  atr  otr exe u N N N Y  otr exe u N N N N Y  otr exe u N N N N N N  exe u N N N N N N N  exe u N N N N N N N  exe u N N N N N N N  exe u N N N N N N N  exe u N N N N N N N N  exe u N N N N N N N N  exe u N N N N N N N N N  exe u N N N N N N N N N N N N N N N N N N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | sir                       | n/atr               | exe           | ns     | 7  | Υ_=   | >    | >   | emn        | Y           |

| otr hil u N N N N Y  otr exe u N N N S Y  asm u N N S Y  asm u N N Y Y  exe usd Y N Y Y  exe usd Y N Y Y  otr exe usd Y N Y  atr/otr/tbc exe usd Y N Y  exe u N N N Y  atr  otr exe u N N N Y  atr  otr exe u N N N Y  exe u N N N N Y  exe u N N N N N  exe u N N N N N N N  exe u N N N N N N N  exe u N N N N N N N N  exe u N N N N N N N N  exe u N N N N N N N N N N N N N N N N N N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ot                        | ı                   | ЫI            | n      | z  | Y     | z    | ×   | scc+gi     | Y           |

| otr hill u N N S Y  otr exe u N N S Y  exe u N N Y Y  exe u N N Y  exe u N N N Y  otr exe u N N N Y  otr exe u N N N Y  otr exe u N N N Y  atr/otr/tbc exe usd Y  exe u N N N Y  exe u N N N Y  exe u N N N N N  exe u N N N N N N  exe u N N N N N N  exe u N N N N N N N  exe u N N N N N N N  exe u N N N N N N N N  exe u N N N N N N N N N N N N N N N N N N                                                                                                                                                                                                                                                                                                                                          | sin                       | m/db                | exe           | n      | Z  | z     | Z    | Y   | tci        | <b>&gt;</b> |

| otr         hill         u         N         S         Y           otr         exe         u         N         N         Y         Y           exe         u         N         Y         Y         Y         Y           exe         u         N         N         Y         Y         Y           exe         u         N         N         Y         Y         Y           otr         exe         u         N         N         Y         Y           atr/otr/tbc         exe         u         N         Y         Y         Y           exe         u         N         N         N         N         N         N           exe         u         N         N         N <td>si</td> <td>m/atr</td> <td>asm</td> <td>n</td> <td>z</td> <td>z</td> <td>z</td> <td>Z</td> <td>scc</td> <td>z</td> | si                        | m/atr               | asm           | n      | z  | z     | z    | Z   | scc        | z           |

| otr exe u N N S Y S C S S S S S S S S S S S S S S S S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Ŧ                         | o/atr/otr           | FI            | n      | z  | z     | S    | Y   | pdi        | Y           |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Ŧ                         | o/atr/otr           | exe           | n      | z  | z     | S    | Y   | ddi        | Y           |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Si                        | п                   | exe           | n      | z  | z     | Y    | Y   | pdi+dcc    | X           |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | at                        | H                   | asm           | n      | z  | $Y_1$ | z    | z   | ang        | z           |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | sir                       | u                   | exe           | n      | z  | z     | Y    | S   | scc        | z           |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Si                        | qp/u                | exe           | psn    | >  | z     | Υ    | Y   | tci        | X           |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $\mathbf{s}$              | m/db                | exe           | n      | z  | z     | z    | Y   | ddi+tci    | X           |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | at                        | <b>L</b>            | exe           | n      | z  | z     | လ    | Z   | ang        | z           |

| (db)otrexeusdYYY(db)atrexeuN $Y_1$ NY(db)atr/otr/tbcexeuY $Y_1$ YYotrexeuYNYYexeuNNNNexeuNYNexeuNYNexeuNYNexeuNYNexeuNYNexeuNYNexeuNYNexeuNYNexeuNYNexeuNYN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | sin                       | n                   | exe           | n      | Y  | Z     | Y    | Y   | emn        | Υ           |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $\dot{s}$                 | m/db/otr            | exe           | psn    | Y  | Z     | Y    | Ā   | ddi        | Y           |

| db/atr/otr/tbc         exe         usd         Y         Y1         Y         Y           otr         exe         u         Y         N         Y         Y           otr         exe         u         N         N         N         N           exe         u         N         Y1         Y         N           exe         u         N         Y1         Y         N           exe         u         N         Y         Y         N           exe         u         N         Y         Y         Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . <u>s</u>                | m/db/atr            | exe           | n      | z  | $Y_1$ | z    | Y   | ddi        | z           |

| otr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | S.                        | $m/db/atr/otr/tb_C$ | exe           | psn    | Υ  | $Y_1$ | ⊁    | Y   | tci        | Y           |

| Otr   exe   u   N   N   N   N   N   N   N   N   N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | S.                        | ш                   | exe           | n      | X  | z     | ×    | Υ   | scc+emn    | Y           |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | a                         | tr/otr              | exe           | n      | N  | N     | Z    | N   | emu+tci+cr | z           |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $\mathbf{s}_{\mathbf{i}}$ | m                   | exe           | n      | Z  | Z     | Z    | N   | opp        | z           |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ē                         | ı,                  | exe           | n      | z  | $Y_1$ | Y    | z   | pdi+dcc    | *.          |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . <u>s</u>                | ш                   | exe           | n      | z  | z     | ≻    | z   | scc        | Z           |

| \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ā                         | Į.                  | asm           | n      | z  | Υ=    | S    | Z   | ang        | Z           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . <u>rs</u>               | sim/db/atr          | exe           | psn    | Y  | Y+    | Y    | Y   | dcc        | Y           |

Table 1 (continued) Summary of some related systems.

| Name                    | Purpose                | Input<br>Rep. | Detail | MD | MP    | Sig. | SMC<br>OK | Technology  | Bugs<br>OK |

|-------------------------|------------------------|---------------|--------|----|-------|------|-----------|-------------|------------|

| MX/Vest [69]            | sim                    | exe           | n      | Z  | Υ=    | X    | Ā         | scc+gi      | Y          |

| Pixie [13]              | atr                    | exe*          | n      | ×  | Z     | Y    | Z         | ang         | z          |

| Pixie-II [47]           | atr/otr/db             | exe*          | ns     | Y  | z     | Υ    | S         | scc         | z          |

| Proteus [9]             | atr                    | hII           | n      | z  | $Y_1$ | Z    | S         | ang         | Z          |

| Purify [33]             | qp                     | exe*          | n      | Z  | Z     | Υ    | Z         | ang         | Y          |

| qp/qpt [49]             | atr/otr                | exe           | n      | z  | z     | z    | Z         | aug         | z          |

| RPPT [18]               | atr                    | ΡΠ            | n      | z  | $Y_1$ | Z    | Z         | ang         | z          |

| SELF [12, 35]           | sim                    | exe           | n      | z  | Z     | Υ    | Y         | dcc         | Υ          |

| SIMICS [50, 51, 52, 53] | $\sin/db/atr/otr/tb_C$ | exe           | psn    | Y  | $Y_1$ | Υ    | Y         | tci+dcc     | Υ          |

| Simon [26]              | atr                    | asm           | n      | Z  | z     | Z    | z         | ang         | z          |

| SoftPC [57]             | sim                    | exe           | p(s)n  | N  | Z     | Ā    | Ā         | gcc         | Y          |

| Spa [40]                | atr                    | exe           | n      | z  | z     | တ    | Y         | ddi         | z          |

| SPIM [34]               | sim/atr                | exe           | n      | z  | Z     | Y    | Z         | pdi         | Y          |

| ST-80 [21]              | sim                    | exe           | n      | Z  | z     | Υ    | Y         | dcc         | Υ          |

| Tango Lite [20, 32]     | atr                    | asm           | n      | N  | $Y_1$ | z    | S         | ang         | z          |

| Tapeworm II [81]        | atr                    | exe           | sn     | Y  | Z     | Y    | Y         | emu         | Y          |

| Fitan [6, 7]            | atr                    | exe           | sn     | Y  | z     | ×    | z         | ang         | z          |

| Trapeds [77, 78]        | atr                    | asm           | sn     | Y  | Υ=    | S    | Z         | ang         | Z          |

| WWT [63]                | atr/otr                | exe           | n      | Y  | Y+    | Υ    | Z         | emu+aug+ddi | Υ          |

| Z80MU [3]               | sim                    | exe           | u(s)   | Z  | Z     | Y    | Y         | ddi         | Y          |

| Shade [16, 17]          | $\sin/atr/otr/tb_C$    | exe           | n      | N  | N     | Y    | Y         | dcc         | N          |

|                         |                        |               |        |    |       |      |           |             |            |

Input Rep. describes the input to the tool. Each tool is a translator that processes an input form; the input affects the tool's portability and also the performance and accuracy (faithfulness) of the resulting code. Processing a highlevel language input (hll) can have the best portability and best optimization but the tool can only be used for source programs written in the supported languages [83] and cannot generally analyze the effects of other translation tools (compilers, etc.). Consuming assembly code (asm) is less portable than a high-level language but can provide more detailed information and allows processing of output from a variety of compilers. To the extent that assembly languages are similar, such tools may be relatively easy to retarget, though detailed information may still be obscured. Finally, using executable code as eliminates the need for access to the source and the (possibly complex) build process. However, information is usually reported in machine units, not source constructs. Some tools use symbol table information to report information symbolically. Others need symbolic information in order to perform translation (exe\*).

Detail describes how much of the machine is simulated. Most tools work with only user-level code (u); some also run system-level code (s); and system-mode simulation generally requires device emulation (d). Some target machines have no system mode, so simulation can avoid the costs of address translation and protection checks; these machines have the system mode marked in parenthesis.

MD reports whether the tool supports multiple protection domains and multitasking (multiple processes per target processor). This usually implies support for system-mode operation and address translation. Target systems that multitask in a single protection domain are listed as N. MP tells whether the tool supports multiple processor execution;  $Y_1$  indicates that the tool uses a single host processor,  $Y_{=}$  indicates that the tool runs as many target processors as host processors, and  $Y_{+}$  that it uses multiple host processors and simulates more target processors than host processors. Simulating a multiprocessor generally introduces additional slowdown at least as big as the number of target processors divided by the number of host processors.

Supporting signals is often difficult since execution can be interrupted at any instruction and resumed at any other instruction, yet analysis and instrumentation may use groups of instructions to improve simulation efficiency. The Sig. column is Y for tools that can handle asynchronous and exceptional events. S indicates that the tool is able to deal with some but not all aspects; for example, signals may be processed so the program's results are correct, but no address trace information is generated.

SMC OK describes whether the tool is able to operate on programs where the instruction space changes dynamically. Dynamic linking is the most common reason, but there are a number of other uses [45]. Static rewrite tools can sometimes (S) dynamically link to statically-rewritten code, but the dynamically-formed link cannot be rewritten statically and thus may go untraced.

Technology describes the general implementation techniques used in each tool [61]. An "obvious" implementation executes programs by fetching, decoding, and then interpreting each instruction in isolation. Most of the implementations optimize by predecoding and then caching the decoded result; by translating to host code to make direct use of the host's prefetch and decode hardware [21]; and by executing target instructions in the context of their neighbors so that target state (e.g. simulated registers) can be accessed efficiently (e.g. from host registers) across target instruction boundaries. The implementations are:

- $\Box$  Hardware emulation, including dedicated hardware and microcode (emu).

- $\Box$  The "obvious" implementation, a decode and dispatch interpreter (ddi).

- □ Predecode interpreters (pdi) that pre-convert to a quick-to-decode intermediate representation or IR. The IR can take many forms; a particularly fast, simple, and common form is threaded code (tci).

- □ Static cross-compilation (scc) which decodes and dispatches during cross-compilation, avoiding essentially all run-time dispatch costs. Note that conversion is limited by what the tool can see statically. For example, dynamic linking may be hard to instrument statically. Limited static information also limits optimization. For example, a given instruction may in practice never be a branch target. Proving that is often hard [49, 55], so the static compiler may be forced to produce overly-conservative code. As a special case, where the host and target are the same, the static compiler merely annotates or augments (aug) the original program with code to save trace data or emulate missing instructions.

- □ Dynamic cross-compilation (dcc) is performed at run time and thus can work with any code including dynamically-linked libraries. Also, dynamic cross-compilers can perform optimistic optimizations and recompile if the assumptions were too strong [16, 35, 36, 42, 55, 52, 66]. However, since the compiler is used at run time, translation must be fast enough that the improved performance more than pays for the overhead of dynamic compilation [16]; in addition, code quality may be worse than that of a static cross-compiler [2, 36, 69] since dynamic code analysis may need to "cut corners" in order to minimize the compiler's running time.

Where interpreter specifics are unavailable the tool is listed as using a general interpreter (gi). Tools listed as aug and emu execute most target instructions using host hardware. Checkpointing and rollback (cr) can be used to simulate speculative execution, in order to trace it's effects [67].

Note that input forms lacking symbolic information – exe especially – can be hard to process statically because static tools have trouble determining what is code and what is data and also have trouble optimizing over multiple host instructions [49, 55]. By contrast, tools that perform dynamic analysis (including both interpreters and dynamic cross-compilers) can discover the program's structure during execution. Translation techniques can be mixed by using one technique optimistically for good performance and another as a fallback when the first fails. However, such implementations have added complexity because they rely on having two translators [2, 51, 52, 69, 82, 83].

Bugs OK describes whether the tool is robust in the face of application errors such as memory addressing errors or divide-by-zero errors. For example, application stores to random addresses may clobber Shade data structures. Typically, checking for addressing errors requires extra checks for every instruction that writes memory. In some systems the checks are simple range checks; tools that support multiple address spaces and sparse address spaces generally require full address translation [4, 53, 65]. Y\* indicates that checking can be turned on but performance is worse.

#### 2.2 Cross-Architecture Simulation

Table 2 summarizes features of cross-architecture simulation tools that use different host and target instruction sets. The Translation Units column shows translation-time tradeoffs between analysis complexity and performance. Assumptions shows assumptions about the relationship between the host and target machines; these assumptions are usually used to simplify and speed up the simulator. Perf. shows the approximate performance as the slowdown of each tool compared to native execution. Notes shows special or missing features of each simulator. The columns are described in detail below.

Translation Units shows the number of (target) instructions that are analyzed and translated at a time. Using bigger chunks reduces dispatching costs and increases opportunities for optimization between target instructions. Larger translation units also typically require better analysis or dynamic flexibility in order to ensure that the program jumps always take a valid path or can

Table 2 Summary of some systems that perform cross-architecture simulation.

| tion.             |                |              |          |                 |

|-------------------|----------------|--------------|----------|-----------------|

| Name              | Translation    | Host/Target  | Perf.    | Notes           |

|                   | Units          | Assumptions  | (est.)   |                 |

| Accelerator [2]   | proc-ip/proc   | nr, bo, pg., | 1.5      | targ. pg.       |

|                   |                | ph, regs     |          | mixed           |

| Cerberus [10]     | i-i/i          |              | 100      |                 |

| Cygnus [30]       | i-i/i          | nr           | 10       | same            |

|                   |                |              | 20       | different       |

| dis+mod+run [27]  | bb-bb/bb       | nr           | 10       |                 |

| Executor [37, 54] | proc-proc/bb   | nr           | 3-10     | targ. pg.       |

| FlashPort [28]    | ip-ip/ip       |              | 1        | hand            |

| g88 [4]           | i-bb/i         | nr, bo       | 30       | targ. pg.       |

| GNU Simulators    | i-i/i          |              | 40       |                 |

| [11, 29]          |                |              |          |                 |

| IMS [39]          | i-i/i          |              | 1        |                 |

| Kx10 [31]         | i-i/i          |              | 200      | targ. pg., ws.  |

| Mable [19]        | i-i/i          |              | 20-80    |                 |

| mg88 [5]          | i-bb/i         | nr, bo       | 80       | targ. pg.       |

| Migrant [68]      | ebb-ip/ebb     | nr, bo       | -        |                 |

| Mimic [55]        | ebb-ib/ib      | nr, bo, regs | 4        | ↓fp, ↓align,    |

|                   |                |              |          | +dcc            |

| Moxie [13]        | bb-bb/bb       | nr           | 2        |                 |

| Mshade [65]       | bb-ebb/ebb     | nr, bo       | 5-10     | same, targ. pg. |

| MX/Vest [69]      | ip-ip/ip       | bo           | 2        | mixed           |

| Self [12]         | ip-ip/ip       | none         | N/A      | VM              |

| SIMICS            | i-bb/i         | nr, bo       | 15-30    | targ. pg.       |

| [50, 51, 52, 53]  |                |              |          |                 |

| SoftPC [57]       |                |              | _        |                 |

| SPIM [34]         | i-i/i          | nr, bo       | 25       |                 |

| ST-80 [21]        | proc-proc/proc | none         | N/A      | VM              |

| Z80MU [3]         | i-i/i          | nr, bo, regs |          | mixed           |

| Shade [16, 17]    | ebb-ib/ebb     | nr, bo       | 1.9-4.9  | same            |

|                   |                |              | 3.3-13.0 | different       |

|                   |                |              |          | (tracing off)   |

gracefully handle unexpected cases that arise from unwarranted optimism [16, 55, 49, 69]. Many tools use larger units for analysis than for translation. This keeps much of the simplicity of smaller translation units but enables optimizations that require broader analysis. Translation units are thus reported as typ.-max./gen., where typ. is the typical unit of analysis, max. is the largest unit of analysis, and gen. is the largest target unit for which host code is generated. For example, Shade mostly uses small units, but analyzes larger units for condition codes, which otherwise become a simulation bottleneck. Shade then uses the results of the sophisticated analysis to generate one of two simple translations: either do or do not save condition codes at the end of a simulated basic block. Translation units include: individual instructions (i), basic blocks (bb), extended basic blocks with a single entry but many exits (ebb), inter-block (ib), procedural (proc), or interprocedural (ip).

Host/Target Assumptions describes assumptions that a tool makes about the similarity of the host and target machines. Assumptions can be used to reduce both the complexity of analysis and the detail of rewriting (translation) and thus the run-time cost. Assumptions include byte ordering (bo); numeric representation (nr), including size and format; the number of registers on the host and target machines (regs), and access to the host machine's privileged hardware (ph) in order to implement system-level simulation.

Perf. is a performance estimate, expressed as the number of (simple) instructions executed per (simple) simulated or traced instruction. A variety of other metrics, such as run-time dilation, might be reasonable, but are typically more dependent on the host and target machine implementations and are thus harder to use when comparing tools [50, 52]. The performance estimates here are necessarily inexact, as they are based on values reported using various metrics and target applications. Note that performance also depends on simulation detail; for example, Shade would be slower if it simulated both user and kernel address spaces. The entry N/A indicates "not applicable" because the target is a virtual machine. A dash (-) indicates unknown or unreported performance. Shade figures are the minimum and maximum over the SPEC92 [22] benchmarks.

Notes describes particular features of the tools: targ.~pg. for detailed memory simulation including simulation of target machine pages; ws. for simulation between machines with incompatible word sizes (e.g. simulating a machine with 9-bit bytes on a machine with 8-bit bytes);  $\downarrow fp$  for simulation that omits floating-point numbers; fp+ for simulation that can be set either to run fast or to faithfully emulate the target machine;  $\downarrow align$  for tools that omit simulation of unaligned accesses; +dcc for dynamic compilers where compile time is not included in the performance but where it would likely have a large effect; VM

for emulation of a virtual machine that has been designed carefully to improve portability and simulation speed; mixed for simulators that can call between host and target code so that the application can, e.g., dynamically link to fast-running host-code libraries; same for figures reported on the same host and target; different for figures reported for cross-execution; and hand for tools that require some human intervention to perform cross-execution.

# 2.3 Comparison to Shade

Shade improves over many other tools by providing their individual features together in one tool, and by providing both detailed control and efficiency that is competitive with the other tools.

Most tools avoid cross-architecture execution or omit some machine features. These choices improve execution efficiency but limit the tool's applicability. Some exceptions are g88 and it's derivatives [4, 5, 50, 51, 52] and SimOS's MSHADE [65], which are somewhat less efficient than Shade and less flexible at tracing, and also Accelerator [2] and MX/Vest [69] which do not perform tracing and which use two translators, one optimistic and one conservative, to achieve high efficiency. Shade supports cross-architecture execution, and faithfully executes important machine features such as signals and self-modifying code (and thus dynamic linking), so it can be used on a wide variety of applications.

Simulators that use dynamic compilation are typically flexible and the compiled code performs well. However, many previous dynamic compilation systems have imposed limitations that Shade eliminates. For example, Mimic's compiler [55] produces high-quality code, but at such expense that overall performance is worse than Shade; Shade reduces compilation overhead by allowing multiple implementations of each application instruction, only optimizing the most common branches, and using a different data structure to minimize the space overhead of branches. MINT [83] is unable to simulate changing code and never reclaims space used by inactive code.

Tracing tools typically produce only address traces, and often run only on the machine for which the trace is desired. Even tools that allow cross-architecture simulation tend to limit the generality of the machine simulation or of the tracing facilities in order to maintain efficiency [27, 34]. Shade supports cross-architecture tracing and simulates user-mode operation in detail. It currently lacks system-mode tracing facilities provided by some other tools though some

of these tools limit machine features and/or require hand-instrumentation of key kernel code. Shade collects more trace information than most other tools, though it lacks the timing-level simulation of mg88 [5] and the simulation and tracing of speculative execution provided by Mime [67]. With Shade, analyzers select the amount of trace data that Shade collects, and analyzers that consume little trace data pay little tracing overhead. Thus, it is typically the analysis tools that limit overall performance.

All of the listed tool building tools permit extended tracing. Shade provides the most efficient yet variable extensibility, and only Shade also inlines common trace operations. Shade analyzers have used both C and C++ as the extension language [58, 59]. We note also that although Shade is not designed for debugging, Shade-V9.V8 has been used as the back end of a debugger [25].

Shade's flexibility and performance does come at a penalty. For example, Shade performs inter-instruction analysis and host code generation; this makes Shade more complex and less portable than, e.g., g88. Shade does not presently simulate multiprocessors or system-mode operation. Though both are limits of the implementation not of the technique, supporting them would make Shade slower since they complicate simulation and enlarge the translated code size in order to, e.g., translate addresses on loads, stores, and so on [4, 53, 65].

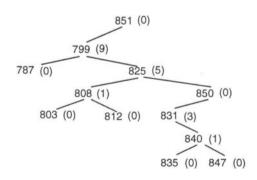

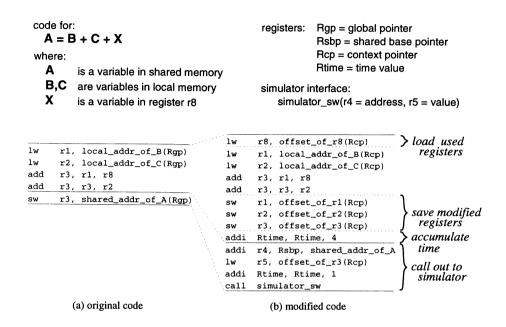

#### 3 ANALYZER INTERFACE